デジタル・ソフトの協調設計(Zynq・Intel SoC)

デジタル・ソフトウエアの双方を理解し、全体を最適化する技術

最近、Xilinx社のZynqやIntel社の SoC FPGAのように、FPGAとCPUを搭載したLSIデバイスが普及しつつあります。 三栄ハイテックスで、FPGAに対してはデジタル設計、CPUに対してはソフトウエア設計をそれぞれ行い、デジタル・ソフトウエアを統合した1つのシステムとして動作させる技術を追求しています。INDEX

デジタル・ソフトウエアの協調設計サービス

従来の設計における問題点

デジタルとソフトウエアを別々に設計して最後につなげて全体が動作すればよしとしてきた従来の設計では、ZynqやIntel SoCが持つポテンシャルを十分引き出せないことも分かってきました。つまり、デジタルとソフトウエアの双方を理解して、両者を一体の1つのシステムとして全体を最適化する技術が必要になってきました。しかし世の中で、そういった技術を持つ技術者はごく少数しか存在しません。

FPGAとCPUを1つのチップにまとめるメリット

従来は別々のチップに分かれていたFPGAとCPUを1つのチップにまとめることによるメリットは、単純に実装面積が小さくなってコンパクトになることだけではありません。通常、FPGA・CPU間の通信は一度チップの外に出て基板(ボード)を介して行いますが、ZynqやIntel SoCではチップ内で完結するようになり通信速度が大きく上がります。その結果、デジタル・ソフトウエアを組み合せて1つの機能を実現するようなシステムでは、通信速度の遅さというこれまでのボトルネックが取り外され、システム全体の処理速度を引き上げることができる可能性(ポテンシャル)が広がりました。

当社では、デジタル・ソフトウエアの協調設計サービスを開発しています。当社単独で実際に需要がありそうなシステムをあらかじめ作って技術を蓄積しておき、具体的なニーズが発生した際にお客様に素早く必要な設計サービスを提供します。

当社では、デジタル・ソフトウエアの協調設計サービスを開発しています。当社単独で実際に需要がありそうなシステムをあらかじめ作って技術を蓄積しておき、具体的なニーズが発生した際にお客様に素早く必要な設計サービスを提供します。

開発事例

画像認識システム

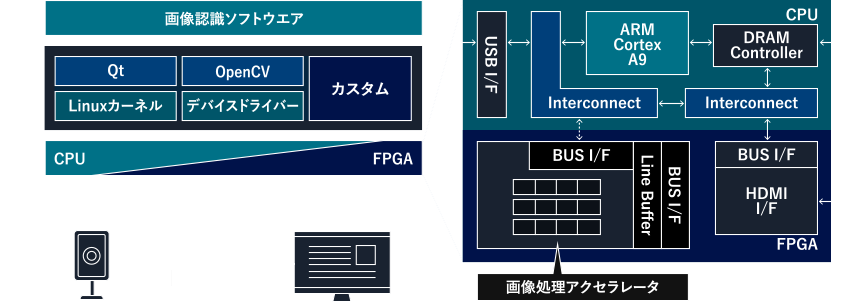

例えば、最近市場が拡大しつつある「画像認識システム」を、下図のような構成で開発しています。

このシステムは、Zedboard(AVNET社製)というZynqの評価用ボードの上に実装しました。

画像認識アルゴリズムの例(円検出)

Zynqの評価用ボード「Zedboard」(AVNET社)

システム全体を最適化し、パフォーマンスを最大限に引き上げる

画像認識アルゴリズムの基本部分はソフトウエアにて処理を行い、処理の一部をデジタル回路へ切り出すことで、高速化を図っています。 ソフトウエアはZynq内のCPU上で、デジタル回路は同じくZynq内のFPGA上で動かします。 アルゴリズムを理解した上で、どこまでをソフトウエアに担わせてどの部分をデジタル回路に持っていくかということを考え、システム全体で最適化してパフォーマンスを最大限に引き上げることが設計の鍵になります。

既存ライブラリー・IPの活用による、開発工数削減

こういったシステムの開発では、全てを一から自前で作らずに、入手可能なライブラリーやIPをできる限り活用して、開発工数(開発期間)を最小限に抑えることも重要な技術です。

例えばこのシステムでは、CPUにLinux-OSを搭載し、ソフトウェアはそのOS上で動かしています。Linux-OSを使うことで、Qt(GUIライブラリーの一種)やOpenCV(画像処理のライブラリーの一種)といった、オープンなプログラミングライブラリーを利用することができます。

さらに、Linux-OSでは各種のデバイスドライバーが用意されているため、USBカメラを接続する場合にも、Linux-OSに含まれるUSBドライバを利用することができ、わざわざUSBインターフェースを独自に用意する必要がありません。FPGA上でも、ソフトウェアでは実現が難しいHDMIなどの高速インターフェースのIPをXilinx社のWebサイトから入手し、搭載しています。ただし、HDMIと画像認識アルゴリズムでは画像の規格が異なるため、規格変換用のデジタル回路を作ってHDMIのIPの手前に挿し込んでいます。

このように、効率的に開発を進めるためには、既存のIPと自前の回路をうまく組み合わせる技術も求められます。

例えばこのシステムでは、CPUにLinux-OSを搭載し、ソフトウェアはそのOS上で動かしています。Linux-OSを使うことで、Qt(GUIライブラリーの一種)やOpenCV(画像処理のライブラリーの一種)といった、オープンなプログラミングライブラリーを利用することができます。

さらに、Linux-OSでは各種のデバイスドライバーが用意されているため、USBカメラを接続する場合にも、Linux-OSに含まれるUSBドライバを利用することができ、わざわざUSBインターフェースを独自に用意する必要がありません。FPGA上でも、ソフトウェアでは実現が難しいHDMIなどの高速インターフェースのIPをXilinx社のWebサイトから入手し、搭載しています。ただし、HDMIと画像認識アルゴリズムでは画像の規格が異なるため、規格変換用のデジタル回路を作ってHDMIのIPの手前に挿し込んでいます。

このように、効率的に開発を進めるためには、既存のIPと自前の回路をうまく組み合わせる技術も求められます。

![[ロゴ]三栄ハイテックス株式会社](/shared/img/logo_w.png)