高性能ADC開発

ユーザー視点から生まれる、高性能ADCの研究開発

自動車の電動化、産業機器のデジタル化、IoTによるセンサーのネットワーク対応を背景に、さまざまなセンサーと併せて使用するADCの需要が高まっています。センサーの高性能化に伴いADCへの性能要求も高まっています。三栄ハイテックスは、センサー性能を十分に引き出すことができるように複数の方式で高性能なADCの開発に取り組んでいます。

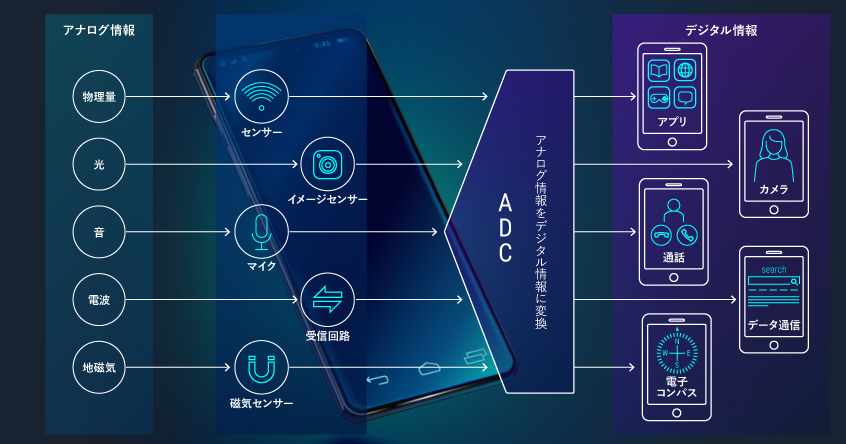

ADCとは

ADCとは、アナログ-デジタル変換器(Analog to Digital Converter)のことです。アナログ信号をデジタル信号に変換するLSIです。身の回りのさまざまな連続的なアナログ信号(音、温度、光など)をデジタル化し、コンピューターやマイクロプロセッサが処理できる形式に変換します。

ADCの活用事例

ADCは、物理的な信号をセンサーで受信した後、デジタル信号として処理する際に欠かせない技術です。近年では、自動車の電動化や産業機器のデジタル化、IoTによるセンサーのネットワーク対応が進み、センサーと連動するADCの需要が増加しています。こうした市場ニーズに対応するため、当社は半導体技術を生かし、高精度・高速・低消費電力を追求したADCの開発に注力しています。特に、次世代のIoTデバイスやAI向けに、高サンプリングレートADCや高分解能ADCの開発を進めています。

三栄ハイテックスのADC開発の強み

三栄ハイテックスは、以下の強みを生かして高品質なADCを開発します。

一貫した社内開発体制

当社は、LSI設計における回路設計からレイアウトまでを社内で完結できるEDA(Electronic Design Automation)ツール・ライセンスを保有しています。これにより、設計・シミュレーション・レイアウトの各工程を迅速かつ安全に進めることが可能です。

多様な半導体プロセスへの対応力

各種ファウンドリやお客さまの内製工場を問わず、多数の半導体プロセスでの開発実績を有しています。PDKのインストールや開発環境の立ち上げにも柔軟に対応し、スムーズな開発を実現します。

ADC研究開発の取り組み

当社は、4つのポイントを軸にADCの研究開発を進めています。

ユーザー視点と最新技術トレンドの反映

当社は、アナログ回路設計やレイアウト設計事業を通じて、多くのお客さまの声を直接伺い、そのニーズを開発に反映しています。 さらに、業界の最新トレンドを取り入れ、実用性と市場要件を兼ね備えた高性能ADCの仕様設計を行います。

高電力効率を実現するADC回路開発

ADCは、変換速度や分解能(SNR)が高くなるほど、消費電力が増加する傾向があります。しかし、高速・高分解能なADCが求められる現代において、低消費電力化は重要な課題です。

当社では、長年培ってきた回路設計技術を駆使し、速度、分解能、電力のバランスを最適化することで、電力効率を最大限に高めるADC開発に取り組んでいます。

当社では、長年培ってきた回路設計技術を駆使し、速度、分解能、電力のバランスを最適化することで、電力効率を最大限に高めるADC開発に取り組んでいます。

小型化(小面積化)の実現

IC内に効率的に組み込むための小型ADCの開発にも注力しています。 設計段階から可能な限りの小型化を追求しています。

迅速な提供体制

当社では、回路設計、レイアウト、評価までを一貫して実施する開発体制を整えています。

この結果、ADCをIP(Intellectual Property)として迅速に提供することが可能です。

お客さまの特定の仕様や要件に合わせたカスタマイズにも柔軟に対応します。

ADC開発実績

当社のADC開発実績を紹介します。

用途に合わせて、さまざまな回路方式のADCに対応した自社開発IPを保有しています。さらに、ADCをICに実装する際に必要となる周辺回路IPも充実させており、お客さまの多様なニーズに応えます。

用途に合わせて、さまざまな回路方式のADCに対応した自社開発IPを保有しています。さらに、ADCをICに実装する際に必要となる周辺回路IPも充実させており、お客さまの多様なニーズに応えます。

| 回路方式 | 主な用途 |

|---|---|

| デルタシグマ(ΔΣ) | 計測器、オーディオ、高精度センサー |

| 逐次比較(SAR) | 汎用、マイコン内蔵、低電力センサー |

| パイプライン(Pipeline) | 産業・医療機器、ビデオ、通信 |

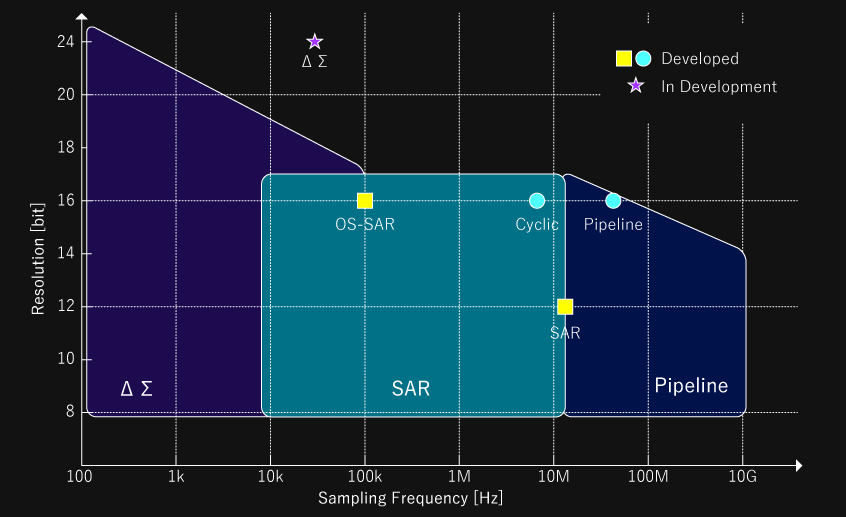

ADCの性能領域と、三栄ハイテックスの開発実績・開発計画

自社開発ADC IPリスト

ADC IPリスト

※ Delta Sigma ADCは現在開発中です。値は目標値になります。

| 要素名 | 内容・性能(設計値) | 特長 |

|---|---|---|

| Pipelined ADC (PLADC) | パイプラインADC 16bit 50MSps SNR=80dB, 3.3V |

|

| Cyclic ADC (CYADC) | サイクリックADC 16bit 8.5MSps SNR=81dB, 3.3V |

|

| SARADC | SAR-ADC 12bit 10Msps SNR69dB, 1.8V |

|

| OS-SAR ADC (SAROS) | Over Sampling - SARADC 16bit 125kSps SNR>84dB, 1.8V |

|

| DeltaSigma ADC (DSADC) | デルタシグマADC 24bit 48kSps SNR>100dB, 1.8V |

|

ADC IP向け周辺IPリスト

| 要素名 | 内容・性能(設計値) | 特長 |

|---|---|---|

| PGA | 許装アンプ+バッファ x1倍~x128倍 |

|

| BGR | 高精度Bandgap 1.0V 0.2% 3.3V |

|

| RCOSC | 高精度RCOSC 5-80MHz 1.5% 1.8V |

|

自社開発ADC IPの特性表

当社は、長年の研究開発と豊富な経験に基づき、独自性の高いADCを開発し、お客さまへ提供しています。

| PLADC | CYADC | SARADC | OS-SARADC | DSADC | |

|---|---|---|---|---|---|

| 開発年 | 2021 | 2021 | 2023 | 2023 | 2024 |

| プロセス(nm) | TSMC 180 | TSMC 180 | TSMC 180 | TSMC 180 | TSMC 180 |

| 電源電圧(V) | 3.3 | 3.3 | 1.8 | 1.8 | 1.8 |

| 分解能(bit) | 16 | 16 | 12 | 16 | 24 |

| 変換速度(sps) | 50M | 8.5M | 10M | 100K | 48K |

| SNR(dBFS) | 80 | 81 | 69 | 79.5 | 100 |

| VREFバッファ有無 | 有 | 有 | 有 | 有 | 有 |

| 状況 | 評価済 | 評価済 | 評価済 | 評価済 | 開発中 |

継続的な技術開発

さらに多くの用途に対応できるように、当社ではより高分解能・高速・低消費電力を目指して、ADCの自社開発を行っています。特に電力効率の改善・低消費電力化はすべてのユーザーが望むものですので、ユーザーの要望を取り入れつつ業界のトレンドに合わせた継続的な改善を進めています。

自社開発ADC IPの提供とプロセスポーティング

当社では、独自に研究開発した高性能なADC IPを提供しています。さらに、お客さまのご要望に応じたプロセスへのポーティングもご利用いただけます。興味をお持ちの方は、ぜひお気軽にお問い合わせください。

評価環境の提供とサポート

当社では、半導体回路設計にとどまらず、IC試作、評価環境の開発、評価までを一貫して行っています。

特にアナログ回路においては、以下の課題が重要です。

これらの要因により、設計通りのデバイス性能を実現することは容易ではありません。

当社では、こうした外部要因を極力排除し、高精度な回路特性を正確に測定するための高度な評価技術を追求しています。

また、仕様やご要望に応じた専用評価環境の構築も承っておりますので、ご相談ください。

評価用回路基板やシステムの詳細は、以下のリンクからご覧いただけます。

特にアナログ回路においては、以下の課題が重要です。

- 素子のミスマッチの影響

- 電源や温度の変化

- 電源や基板のノイズの影響

- 寄生抵抗や寄生容量の影響

これらの要因により、設計通りのデバイス性能を実現することは容易ではありません。

当社では、こうした外部要因を極力排除し、高精度な回路特性を正確に測定するための高度な評価技術を追求しています。

また、仕様やご要望に応じた専用評価環境の構築も承っておりますので、ご相談ください。

評価用回路基板やシステムの詳細は、以下のリンクからご覧いただけます。

![[ロゴ]三栄ハイテックス株式会社](/shared/img/logo_w.png)