Mixed-Signal LSI デジタル部設計

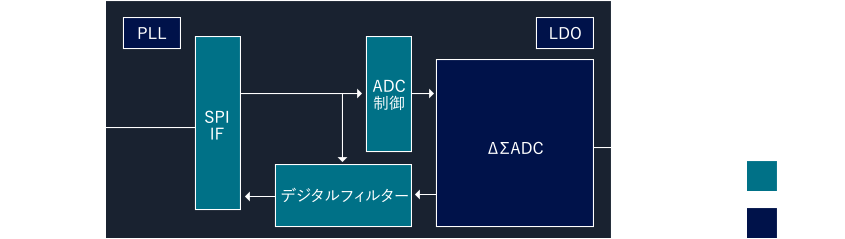

⊿Σ型ADCなどのMixed-Signal LSIにおける、デジタル部の論理設計の事例です。

システム概要

システム要件

⊿Σ型ADCなどのMixed-Signal LSIにおける、デジタル部の論理設計の事例です。

お客さまのご要望

- アナログ・デジタル協調設計により目標性能を満たすこと。

- 省電力化、ICテスト手法を考慮してチップ設計すること。

- デジタル部機能例

- デジタルフィルター、シリアルIF(I2C, SPI)、ADC制御

- シーケンス制御、NVメモリ制御(eFUSE, OTP)

提案内容(特徴)

アナログ回路設計者と連携して、ターゲットとなる性能・チップサイズ・消費電力を満たすよう、全体をシステムとして考えて設計しました。流用設計による開発が主流のため、ベースとなるICの仕様および設計資産を十分理解し、設計・検証の差分を抽出して対応した点も特徴です。

- アナログ部テストモード制御、SCAN設計ルール対応、内蔵eFuse W/Rモードなどのテスト設計を提案。

- アナログ協調設計を考慮して、RTL設計部とゲート設計部を切り分けるなど、柔軟な設計手法で対応。

- 検証用ADCモデルを含むデジタル部のみの検証環境を構築し、検証作業を効率化。

![[ロゴ]三栄ハイテックス株式会社](/shared/img/logo_w.png)