パイプラインADC/サイクリックADCの開発

高性能ADCの開発

当社では世界水準の半導体設計を行うために研究開発を行っています。高性能ADCの開発の様子を紹介します。多様なセンサーに対応するADCのTEG開発

当社では多様なセンサーに対応するADC(Analog to Digital Converter)の開発を行っています。ADCは物理的なアナログ信号をセンサーで受信した後、デジタル信号として処理を行う前に必要な回路です。

2020年より開発を行っていた16bitパイプラインADC/サイクリックADCのTEGが出来上がり、評価基板上にて評価が終了しました。その様子を紹介します。

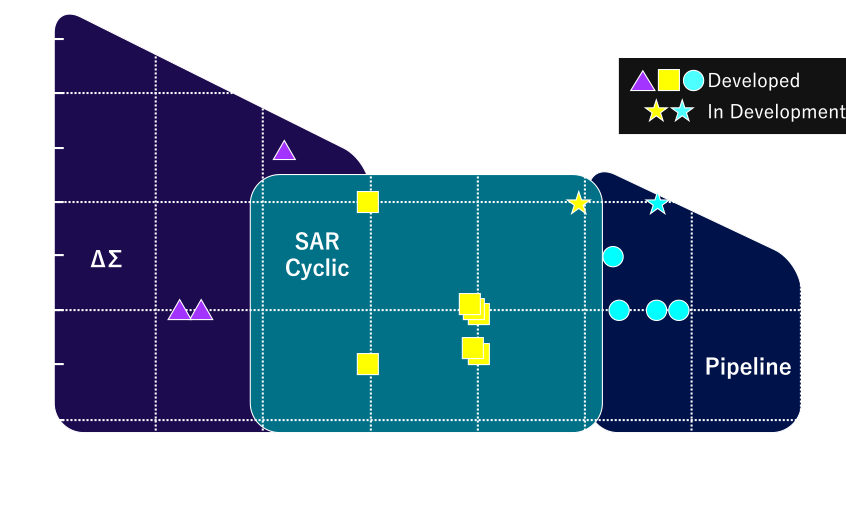

開発を行ったのは下の図の★印の性能のADCです。グラフの右側/上側に行くほど高性能で高価なADCとなります。

ADCの性能領域と、三栄ハイテックスの開発実績・開発計画

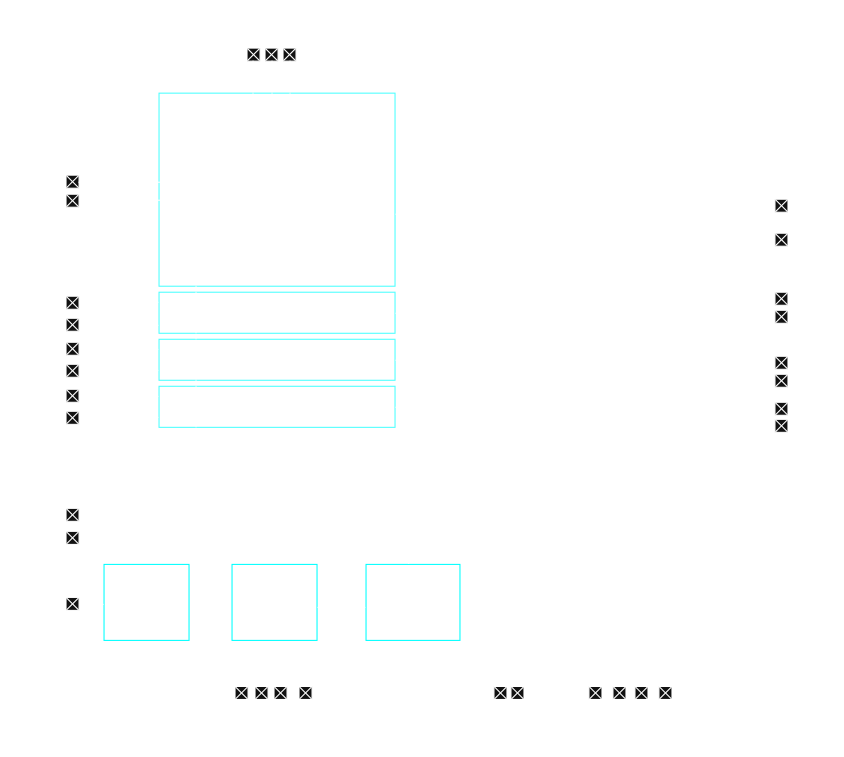

開発したADCのTEGには以下の回路ブロックを組み込みました。

| パイプラインADC |

|

|---|---|

| サイクリックADC |

|

| ADC用クロック系 |

|

| 高精度基準電圧 |

|

どの回路ブロックも、これまでの当社設計実績に対して大幅な性能向上を狙っています。

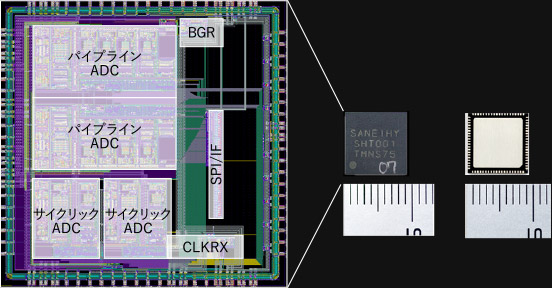

試作TEGの概要

開発したADCのTEGは、当社内にてチップ全体を設計し、レイアウトまで行っています。2021年3月にテープアウト(製造工程への出荷)しました。

試作したADCのTEGの概要です。

搭載している主要回路ブロックです。

- TSMC 0.18um

- ADC合計4ch搭載

- パッケージ 9mm 80pin QFNパッケージ

搭載している主要回路ブロックです。

| パイプラインADC 2ch | 16bit、50Msps、SNR>80dB |

|---|---|

| サイクリックADC 2ch | 16bit、8.5Msps、SNR>80dB |

| 高精度 基準電圧回路(BGR) | 温特トリミング、±0.2%以下 |

| SPI/IFと1024bitレジスタ | TEGコントロール用レジスタ |

| クロックレシーバー(CLKRX) | ADC用差動クロックレシーバー、低ジッタ+Duty補正 |

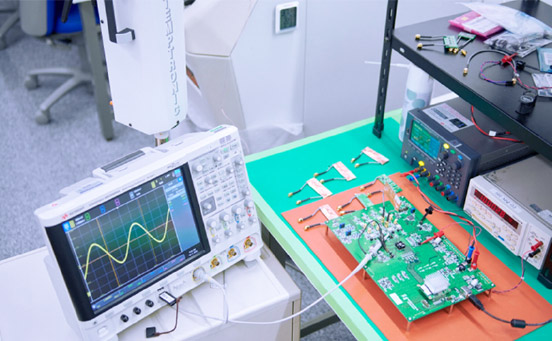

評価環境の立ち上げ

当社独自の評価環境を開発しました。データ収集/分析を高速化するためにFPGAを用います。

開発した評価環境の特徴です。

開発した評価環境の特徴です。

- 16bit 50Msps SNR>80dB のADCの評価を行える

- DC特性(INL、DNL等)、AC特性(SNR、SNDR、SFDR等)共に測定できる

- FPGA+PCソフトによる制御で、高速評価

- 1測定時間が数秒~1分程度

- 外付けの評価機材を少なく

- DC電源1台とPCで動作可能

Pythonで評価ソフトを作成しました。

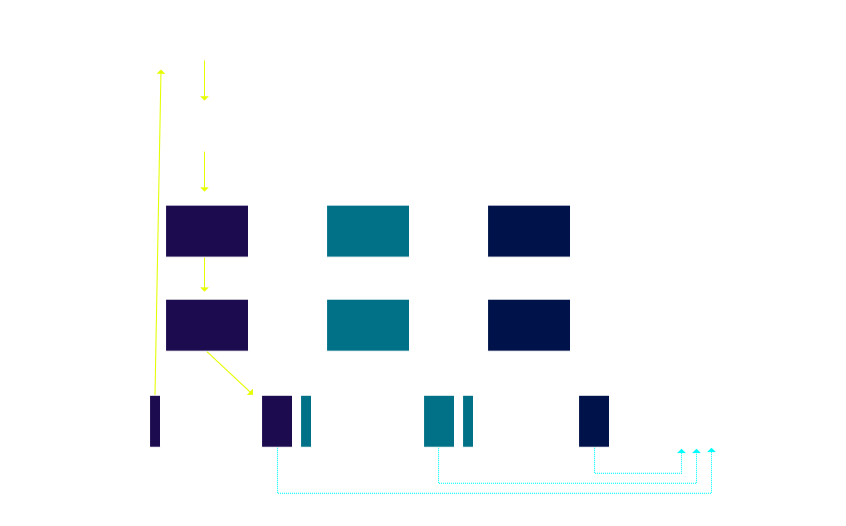

INL/DNL測定時(Rampモード)の動作イメージを例に評価環境の動作を説明します。

評価ソフトを実行した場合の動作

INL/DNL測定時(Rampモード)の動作イメージを例に評価環境の動作を説明します。

評価ソフトを実行した場合の動作

- PCのコマンドラインからPythonソフトを起動

- 評価ボードとUSB通信を開始し、初期設定を行う

- 以下の動作を指定回数(図では3回)繰り返す

- FPGAの測定開始レジスタに1を書き込む

- FPGAがRampデータを生成し、DAC入力データを送る

~65536までコードをカウントアップ - DACがRamp波を出力し、Ampを通してTEGのADCへ入力

- ADC出力コードをFPGAが受信

- FPGAが結果を順番に評価ボード上のDRAMに格納する

- 65536回分のデータがそろったら測定修了し、USB経由でPCはデータをまとめて読み込む

- 測定データを集計し、平均化などの統計処理を行う

- 結果をcsvファイルに出力

- csvファイルをExcelで読み込んでINL/DNLを計算

評価結果

2021年11月よりTEGの評価を行いました。

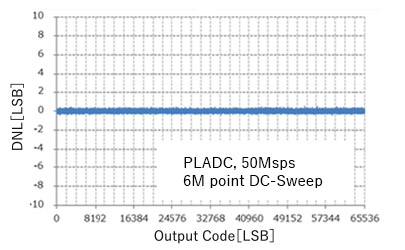

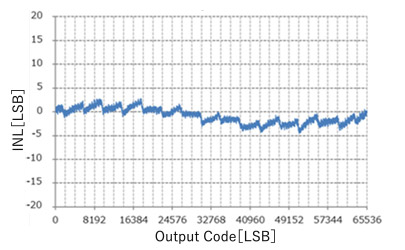

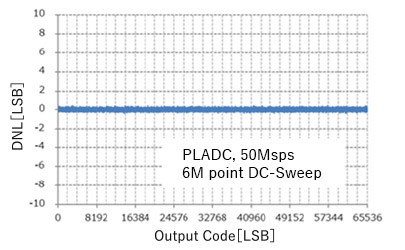

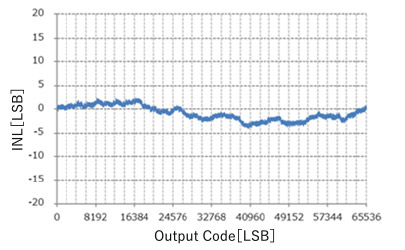

DC特性(INL/DNL)の測定結果

DC特性(INL/DNL)の測定結果です。

- DACを使ってRamp波入力モードで測定

- 65536点をスイープ、100回の平均

パイプラインADC CH2

DNL - Output Code

INL - Output Code

サイクリックADC CH4

DNL - Output Code

INL - Output Code

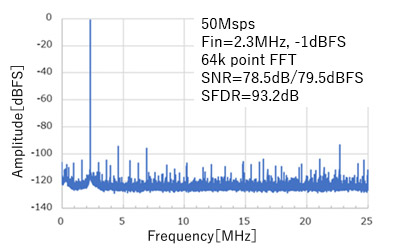

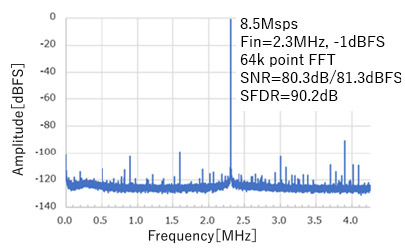

AC特性(SNR/SFDR)の測定結果

AC特性(SNR/SFDR)の測定です。

- DDSを用いて正弦波入力モードで測定

- 65536点FFT、20回平均

パイプラインADC CH2

FFT(PLADC)

サイクリックADC CH4

FFT(CYADC)

評価の結果、おおむね目標仕様通りでした。設計値と評価値の差を分析して、次回の設計に反映します。

高性能なパイプラインADC/サイクリックADCの開発と評価を行いました。半導体回路の設計だけでなく、実際にIC試作を行い、評価環境の開発、評価までを実施ました。

当社の得意とするアナログ回路では、素子のミスマッチの影響、電源や基板のノイズの影響、寄生抵抗や寄生容量の影響などにより設計値通りのデバイス性能を実現することが難しい分野です。外部環境の影響を極力排除する技術を追求し、実際に評価で確認することは、世界水準の技術の研究開発はかかせません。変化の激しい半導体業界の未来を見定め、皆さまの期待に応えていきます。

私たちと一緒に開発に携わるエンジニアを募集しています。

当社の得意とするアナログ回路では、素子のミスマッチの影響、電源や基板のノイズの影響、寄生抵抗や寄生容量の影響などにより設計値通りのデバイス性能を実現することが難しい分野です。外部環境の影響を極力排除する技術を追求し、実際に評価で確認することは、世界水準の技術の研究開発はかかせません。変化の激しい半導体業界の未来を見定め、皆さまの期待に応えていきます。

私たちと一緒に開発に携わるエンジニアを募集しています。

![[ロゴ]三栄ハイテックス株式会社](/shared/img/logo_w.png)