中学生でもわかる!2ナノ半導体とは?

2025年01月15日

- LSI設計

ニュースでよく取り上げられている「2ナノ半導体」を、みなさんはご存じですか? 簡単に言うと「2ナノメートルという超極細の半導体素子で作る電子回路」のことです。 難しそうな名前ですが、私たちの日常生活に大きく関わっています。 今回は、この「2ナノ半導体」について、分かりやすく説明します。

ナノメートルとは

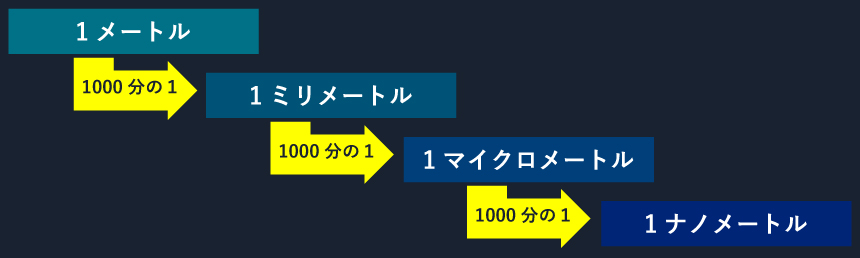

ナノとは、ある量を表すときの単位につける接頭語の1つです。「10億分の1」または「10のマイナス9乗」を意味します。ナノメートルは、SI(国際単位系)基本単位である「メートル」の1ナノ(10億分の1メートル)を表す単位です。

まず、mm(ミリメートル)は1000分の1m(メートル)を表します。「ミリ」は 10のマイナス3乗を意味します。

次に、mm(ミリメートル)の1000分の1をμm(マイクロメートル)と呼びます。μ(マイクロ)は 10のマイナス6乗を表します。

そして、μm(マイクロメートル)の1000分の1をnm(ナノメートル)と呼びます。

※ μm(マイクロメートル)は、かつて「μm(ミクロン)」とも呼ばれていました。

まず、mm(ミリメートル)は1000分の1m(メートル)を表します。「ミリ」は 10のマイナス3乗を意味します。

次に、mm(ミリメートル)の1000分の1をμm(マイクロメートル)と呼びます。μ(マイクロ)は 10のマイナス6乗を表します。

そして、μm(マイクロメートル)の1000分の1をnm(ナノメートル)と呼びます。

※ μm(マイクロメートル)は、かつて「μm(ミクロン)」とも呼ばれていました。

図1. ナノメートルとは

2nm(ナノメートル)は、「10億分の2m(メートル)」または「100万分の2mm(ミリメートル)」「1000分の2μm(マイクロメートル)」という非常に短い長さを表しています。

実際のモノで表現すると、日本人女性の髪の太さは平均で 0.08mmです。これは、80μmまたは8万nmに相当します。つまり、2nmは、髪の毛の細さの4万分の1にあたります。もしも、髪の毛が400mの太さだとしたら、2nmは1cmに相当します。

ウイルスの大きさはおよそ「1万分の1mm」と言われていますので、2nmはウイルスよりもさらに小さく、その長さはウイルスの50分の1です。2ナノメートルの超極細さがイメージしやすくなるかと思います。なお、2nmは20Å(オングストローム)に相当します。オングストロームは、原子や分子の大きさを表す単位として教科書などにも出てきます。

実際のモノで表現すると、日本人女性の髪の太さは平均で 0.08mmです。これは、80μmまたは8万nmに相当します。つまり、2nmは、髪の毛の細さの4万分の1にあたります。もしも、髪の毛が400mの太さだとしたら、2nmは1cmに相当します。

ウイルスの大きさはおよそ「1万分の1mm」と言われていますので、2nmはウイルスよりもさらに小さく、その長さはウイルスの50分の1です。2ナノメートルの超極細さがイメージしやすくなるかと思います。なお、2nmは20Å(オングストローム)に相当します。オングストロームは、原子や分子の大きさを表す単位として教科書などにも出てきます。

半導体とは

半導体について簡単に説明します。ここでは、「スイッチ」をイメージしてください。

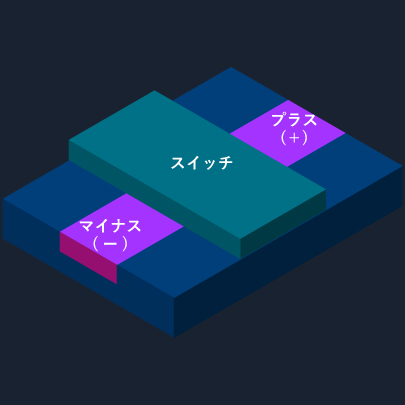

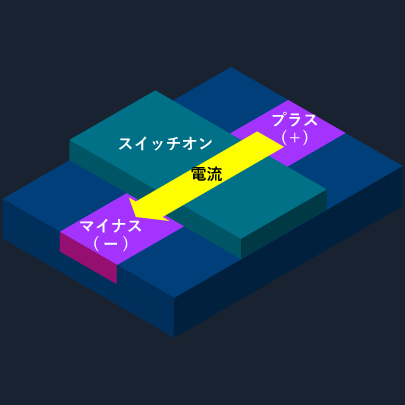

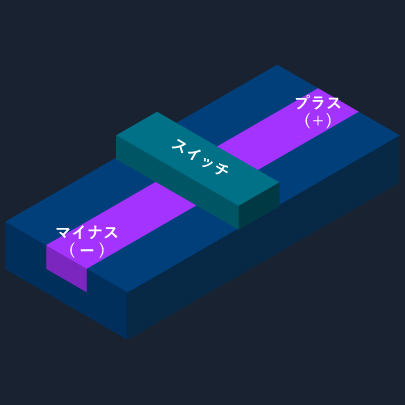

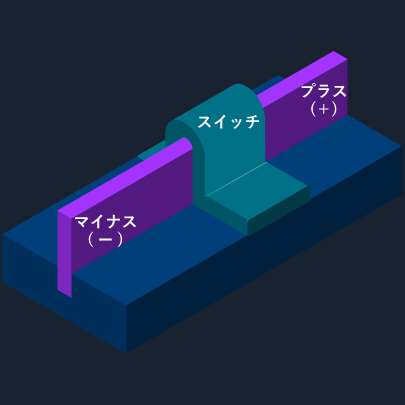

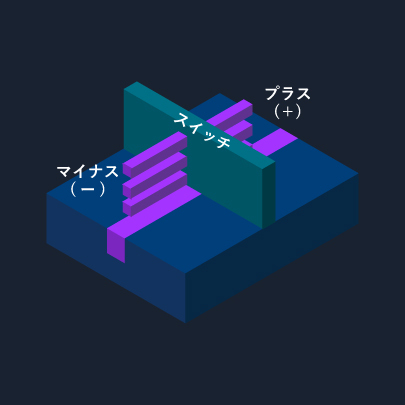

下の図は、半導体素子で作ったスイッチです。図2はスイッチがオフで、電流は流れません。図3では、スイッチがオンで、プラス(+)からマイナス(-)へ電流が流れます。

下の図は、半導体素子で作ったスイッチです。図2はスイッチがオフで、電流は流れません。図3では、スイッチがオンで、プラス(+)からマイナス(-)へ電流が流れます。

図2.MOSトランジスタ(スイッチオフ)

図3.MOSトランジスタ(スイッチオン)

この「スイッチ」を「トランジスタ」と呼びます。トランジスタとは、「動く抵抗」という意味の造語です。このタイプのトランジスタをMOSFET(モスエフイーティー)と言います。

半導体とナノメートル

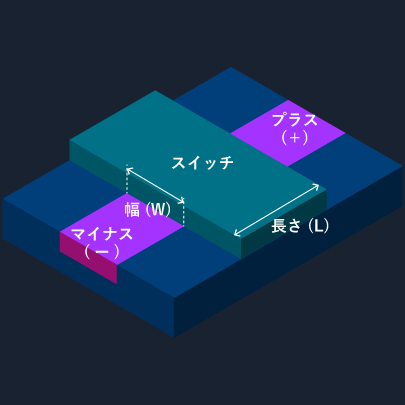

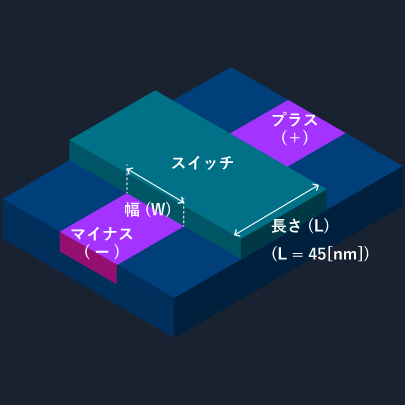

なぜ半導体で「細さ」が重要なのかというと、トランジスタには図4のように長さ(L)と幅(W)が存在するからです。

この長さ(L)と幅(W)は、ひとつのトランジスタの「大きさ」を表します。(性能も表しますが、ここでは触れません)

この長さ(L)と幅(W)は、ひとつのトランジスタの「大きさ」を表します。(性能も表しますが、ここでは触れません)

図4. MOSトランジスタ 長さ(L)と幅(W)

この長さ(L)や幅(W)を、nm(ナノメートル)やμm(マイクロメートル)などの「単位」で表します。半導体の製造工程を「プロセス」と呼びますが、その中でトランジスタの長さ(L)の最小値が重要です。この値は、トランジスタをどれだけ小さく作ることができるかを示す基準です。プロセスにはトランジスタの長さ(L)の最小値があり、「最小値よりも短い長さ(L)のトランジスタを作ってはいけない」というルールがあります。そのため、プロセスの名称にはトランジスタの長さ(L)が使われます。

例えば、45ナノプロセスはトランジスタの長さ(L)の最小値が45nmで半導体を製造することを意味します。

例えば、45ナノプロセスはトランジスタの長さ(L)の最小値が45nmで半導体を製造することを意味します。

図5. 45ナノプロセス MOSトランジスタ

「ナノプロセス」のように、長さ(L)を含めて半導体の微細化を表す指標を「プロセスノード」といいます。プロセスノードの数字が小さくなるほど、より多くのトランジスタをチップ上に配置でき、性能や効率が向上します。半導体とプロセスでも説明しますが、長さ(L)を使ったプロセスノードは、ある時点から使われなくなります。

半導体と電子回路

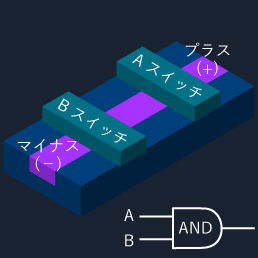

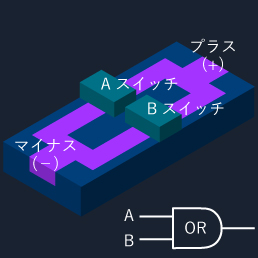

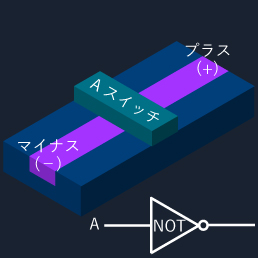

トランジスタを組み合わせることで、デジタル回路やアナログ回路といった電子回路を作ることができます。 ここでは、デジタル回路で使う論理素子について簡単に説明します。 トランジスタを図6、7、8のように組み合わせると、デジタル回路の基本となる3つの論理素子、AND(アンド)、OR(オア)、NOT(ノット)の素を作ることができます。

図6.論理素子 AND

図7.論理素子 OR

図8.論理素子 NOT

原理的には、この3つの論理素子を組み合わせることで、あらゆるデジタル回路を作ることができます。例えば、加算回路や乗算回路、除算回路、比較回路などです。皆さんのパソコンやスマホに入っている「CPU(シーピーユー)」も、これらの回路を組み合わせて作られています。CPUはCentral Processing Unitの略で、「中央演算装置」という意味です。

加算回路を論理素子で組んだ例

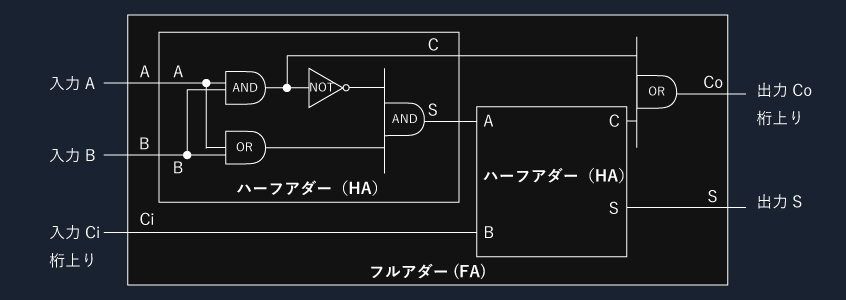

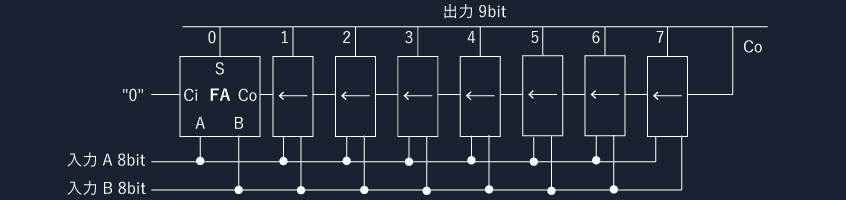

図9. ハーフアダー(HA)回路とフルアダー(FA)回路

図10. 8bit 加算回路

図9、図10の仕組みを簡単に説明します。

| 入力信号 | 加算する8bitのデジタル信号 AとB を入力します。 |

|---|---|

| ハーフアダー(HA) |

|

| フルアダー(FA) |

|

| 8bit 加算回路 | フルアダー(FA)8個を桁上がりで連結した回路です(図10)。 入力A 8bitと入力B 8bitを加算して、桁上がり1bitを含めた9bitの値を出力します。 |

本物の回路は非常に複雑ですが、ここでは原理を説明しました。半導体はLSI(大規模集積回路)として、皆さんが使っているテレビやエアコンなどの電子機器に入っています。そのLSIには、指先に乗るほど小さい数mm角のシリコンチップが含まれています。そのシリコンチップの表面には、トランジスタによって構成された電子回路がぎっしりと詰め込まれています。

半導体とプロセス

半導体の歴史には、プロセス技術の進化があります。プロセス技術とは、半導体を「いかに小さく、いかに高性能に作れるか」を追求する技術のことです。1960年代に誕生した半導体は、長い歴史を経てどんどん小さく高性能になっていきます。

ここでは、インテル社のCPUを例に、その進化を紹介します。

ここでは、インテル社のCPUを例に、その進化を紹介します。

| 西暦 | プロセスノード | CPU名 | トランジスタ数 |

|---|---|---|---|

| ミクロンの時代 | |||

| 1971 | 10μm | 4004 | 2,300トランジスタ |

| 1974 | 6μm | 8080 | 6,000トランジスタ |

| 1976 | 3μm | 8085 | 6,500トランジスタ |

| 1978 | 3μm | 8086 | 29,000トランジスタ |

| 1982 | 1.5μm | 80286 | 134,000トランジスタ |

| 1985 | ~1μm | Intel386 | 275,000トランジスタ |

| サブミクロンの時代 | |||

| 1989 | ~0.6μm | Intel486 | 1,200,000トランジスタ |

| 1993 | ~0.35μm | Pentium | 3,100,000トランジスタ |

| ディープサブミクロンの時代 | |||

| 1997 | ~0.18μm | Pentium Ⅱ | 7,500,000トランジスタ |

| 1998 | ~45nm | Celeron | |

| 1999 | ~0.13μm | Pentium Ⅲ | 9.500,000トランジスタ(512KB L2キャッシュ 25,000,000トランジスタを除く) |

| 2001 | ~90nm | Itanium | |

| 2006 | ~45nm | インテルCore2 Duo | |

| FinFETの時代 | |||

| 2012 | 22nm | 第3世代インテルCore(3次元トライゲート・トランジスタ/FinFET) | |

| 2014 | 14nm | インテルCore M | |

| 2019 | 10nm | 第10世代 インテルCore | |

インテル株式会社.「インテルのあゆみ」.https://www.intel.co.jp/content/dam/www/central-libraries/jp/ja/documents/2022-05/history-of-intel-jp.pdf,(参照 2024-07-19)

Wikipedia.「Pentium III」.https://en.wikipedia.org/wiki/Pentium_III,(参照 2024-07-19)

※ 「~」:それよりも大きなプロセスノードでも生産されていることを意味します。

Wikipedia.「Pentium III」.https://en.wikipedia.org/wiki/Pentium_III,(参照 2024-07-19)

※ 「~」:それよりも大きなプロセスノードでも生産されていることを意味します。

トランジスタの構造が従来の図11に示すMOSFETから、図12に示すFinFETへと移行し始めます。

図11. プレーナ型 MOSFET

図12. FinFET

今後、半導体メーカーは10nm、7nm、3nm、2nm(20Å)、1nm(10Å)というプロセスの進化を目指しています。

3nmプロセスまでは、多くのファウンドリにおいてFinFETが主流のトランジスタ構造として広く採用されてきました。2nmプロセスからは、図13に示すGAA(Gate-All-Around)構造への移行が進んでいると予想されています。

3nmプロセスまでは、多くのファウンドリにおいてFinFETが主流のトランジスタ構造として広く採用されてきました。2nmプロセスからは、図13に示すGAA(Gate-All-Around)構造への移行が進んでいると予想されています。

図13. GAA

トランジスタの構造もいろいろ変わっていくでしょう。

2024年には、3nm程度まで微細化が進んでいます。この「3nm」というプロセスノードの名称は、FinFETという3次元構造のトランジスタが主流になって以降、トランジスタの物理的な長さ(L)を直接的に表すものではなくなりました。現在では、3nmプロセスに相当する性能や微細化のレベルを実現していることを示しているようです。

おそらく今後、プロセスノードの名称に「長さ」を使用することはなくなっていくでしょう。インテル社では、Intel7やIntel3といったプロセスノード名を使っています。

2024年には、3nm程度まで微細化が進んでいます。この「3nm」というプロセスノードの名称は、FinFETという3次元構造のトランジスタが主流になって以降、トランジスタの物理的な長さ(L)を直接的に表すものではなくなりました。現在では、3nmプロセスに相当する性能や微細化のレベルを実現していることを示しているようです。

おそらく今後、プロセスノードの名称に「長さ」を使用することはなくなっていくでしょう。インテル社では、Intel7やIntel3といったプロセスノード名を使っています。

2ナノ半導体のすごさ

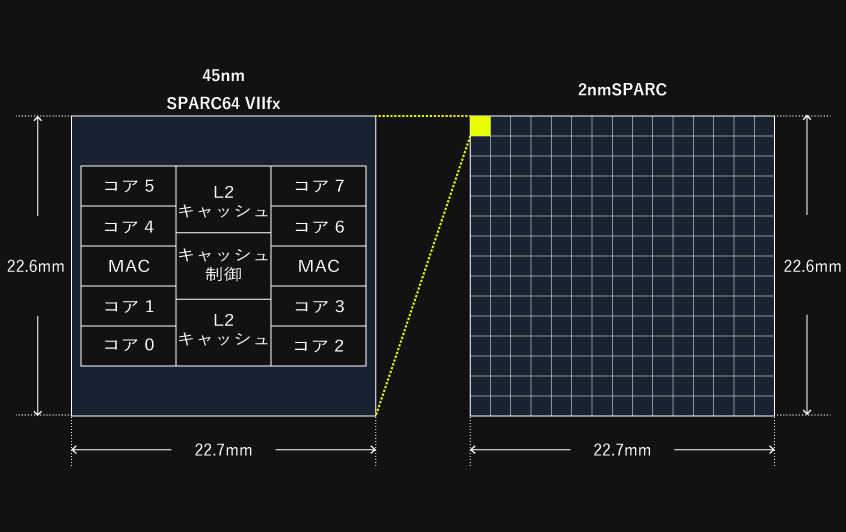

2019年8月に運用が終了したスーパーコンピューター「京(けい)」の処理性能は、10.51PFLOPS(ペタ フロップス)です。「FLOPS(フロップス)」は、コンピューターの処理能力を表す指標で「1秒間に処理できる浮動小数点数演算の回数」を示しています。「P(ペタ)」は「10の15乗(1,000兆)」という意味で、10.51PFLOPSは「1秒間に10,510兆回(≒ 1 京回)処理できる」です。「京」という名前の由来です。50m×60mという大きな「京」の部屋には、864個のラックが並んでいます。ラックひとつひとつに演算装置、通信装置、記憶装置、冷却装置、電源などの機能が入っていて、演算装置には、SPARC64 VIIIfx(以下、SPARCと呼びます)というCPUが102個使われています。「京」全体のSPARCの数は、88,128個です。

Wikipedia.「京 (スーパーコンピューター)」.https://ja.wikipedia.org/wiki/京_(スーパーコンピューター),(参照 2024-12-17)

SPARC64 VIIIfx(SPARC スパーク)

| プロセスノード | 45nm |

|---|---|

| チップサイズ | 22.7mm×22.6mm(約513mm2) |

| トランジスタ数 | 約7億6000万 |

| トランジスタ密度 | 1mm2あたり約150万トランジスタ |

| 処理性能 | 128GFLOPS(ギガ フロップス)「G(ギガ)」は「10の9乗(10億)」 |

富士通株式会社.「スーパーコンピュータ「京」のCPU SPARC64 VIIIfx」.https://www.fujitsu.com/downloads/JP/archive/imgjp/jmag/vol63-3/paper04.pdf, (参照 2024-11-26)

128GFLOPS×88,128個は約11.28PFLOPS(=理論効率)で、「京」の処理性能とほぼ一致します。理論的には、CPUの処理能力×個数が、おおよその全体の処理能力となります。主題の2ナノプロセスのトランジスタ密度は、1mm2あたり約3億3333万トランジスタと言われています。

ANANDTECH.「IBM Creates First 2nm Chip」.https://www.anandtech.com/show/16656/ibm-creates-first-2nm-chip,(参照 2024-12-17)

では、45nmプロセスのSPARCひとつの面積513mm2に、2ナノプロセスではSPARCがいくつ入るでしょうか?

= 2ナノプロセスのトランジスタ密度×513mm2÷SPARCのトランジスタ数

= 3億3333万トランジスタ/mm2×513mm2÷7億6000万トランジスタ

≒ 225個

2ナノプロセスでは、513mm2の中に 225個のSPARCを入れることができます。言い換えれば、225倍の機能が同じ面積に入ります。

= 2ナノプロセスのトランジスタ密度×513mm2÷SPARCのトランジスタ数

= 3億3333万トランジスタ/mm2×513mm2÷7億6000万トランジスタ

≒ 225個

2ナノプロセスでは、513mm2の中に 225個のSPARCを入れることができます。言い換えれば、225倍の機能が同じ面積に入ります。

ここでは、SPARCを225個詰め込んだチップを「2nmSPARC(ナノ スパーク)」と呼ぶことにします。

2nmSPARCの処理能力は、およそ28.8TFLOP(テラ フロップス)です。「テラ」は「10の12乗(1兆)」です。

具体的な大きさを比較してみます。もし、2nmSPARCでスーパーコンピューター「京」を作ったら、どのくらい小さくできるでしょうか?

SPARCを88,128個使っている「京」の処理性能を、2nmSPARCであれば391個で実現できます。ラックの構造は「京」のままで、ひとつのラックに102個の2nmSPARCを使うと、ラックの数を864ラックから4ラックに減らすことができます。50m×60mの「京」の部屋に27個×32個のラックが配置されているとすると、ひとつのラックの領域は1.85m×1.87mです。2nmSPARCのラックを2個×2個で配置すると、部屋の広さは3.7m×3.74mで済みます。

同じ機能で、面積が216分の1になります。「50メートル四方の巨大な機能を、わずか4メートル四方で実現する」これが「2ナノ半導体のすごさ」です。

2nmSPARCの処理能力は、およそ28.8TFLOP(テラ フロップス)です。「テラ」は「10の12乗(1兆)」です。

具体的な大きさを比較してみます。もし、2nmSPARCでスーパーコンピューター「京」を作ったら、どのくらい小さくできるでしょうか?

SPARCを88,128個使っている「京」の処理性能を、2nmSPARCであれば391個で実現できます。ラックの構造は「京」のままで、ひとつのラックに102個の2nmSPARCを使うと、ラックの数を864ラックから4ラックに減らすことができます。50m×60mの「京」の部屋に27個×32個のラックが配置されているとすると、ひとつのラックの領域は1.85m×1.87mです。2nmSPARCのラックを2個×2個で配置すると、部屋の広さは3.7m×3.74mで済みます。

同じ機能で、面積が216分の1になります。「50メートル四方の巨大な機能を、わずか4メートル四方で実現する」これが「2ナノ半導体のすごさ」です。

ここでは面積の比較にとどまり、CPUアーキテクチャ、メモリ配置、消費電力、発熱量など、他の要素は考慮していません。

当社は現時点では2ナノ半導体など、最先端技術の開発には携わっていませんが、2nmSPARCのような先端半導体開発への取り組みは、私たちの目標のひとつです。

当社は現時点では2ナノ半導体など、最先端技術の開発には携わっていませんが、2nmSPARCのような先端半導体開発への取り組みは、私たちの目標のひとつです。

半導体プロセスが進化するということは、チップが小さくなり、より多く生産できるだけでなく、チップの性能や電力効率も向上します。

これにより、お客さまに対して、高性能、高機能、省電力、省スペースな製品を、同じ価格かそれより安く提供することができます。当社も半導体業界の一員として、この進化に乗り遅れることなく、この「価値」をお客さまへ提供し続けてまいります。

これにより、お客さまに対して、高性能、高機能、省電力、省スペースな製品を、同じ価格かそれより安く提供することができます。当社も半導体業界の一員として、この進化に乗り遅れることなく、この「価値」をお客さまへ提供し続けてまいります。

![[ロゴ]三栄ハイテックス株式会社](/shared/img/logo_w.png)