高校生でもわかる!3ナノ半導体

2026年02月12日

- LSI設計

「3ナノ半導体」がニュースでよく取り上げられています。

好評をいただいている「中学生でもわかる!2ナノ半導体とは?」を基にして、少しレベルを上げた高校生クラスで「3ナノ半導体」について解説します。

好評をいただいている「中学生でもわかる!2ナノ半導体とは?」を基にして、少しレベルを上げた高校生クラスで「3ナノ半導体」について解説します。

INDEX

ナノメートル

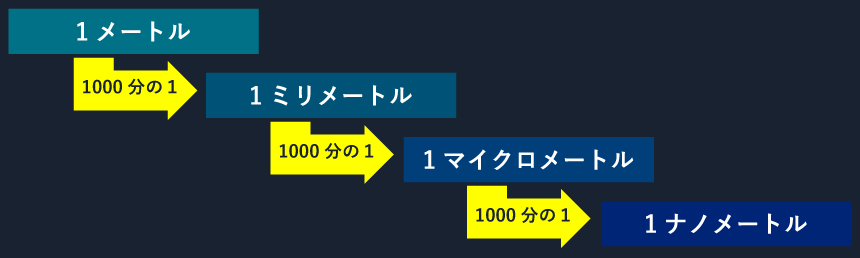

3nm(ナノメートル)は、「100万分の3mm(ミリメートル)」です。およそ「1万分の1mm」と言われるウイルスの、さらに30分の1ほどの超極細が3ナノメートルのイメージです。

図1 ナノメートル

3ナノ半導体

3ナノメートルの意味

「中学生でもわかる!2ナノ半導体とは?」でも書いたように、「3ナノメートル」は 、今までの性能の表し方でいうと"3ナノメートルのプロセスに相当する" という意味で使われています。ひとつずつ説明します。

MOSFET(モスエフイーティー)

半導体トランジスタには多くの種類がありますが、広く長く普及してる代表的なトランジスタは「MOSFET」です。

MOSFETの最大の特徴は「小さくできる」ことです。ここ50年の間にプレーナ型MOSFETが劇的な微細化を遂げてきました。

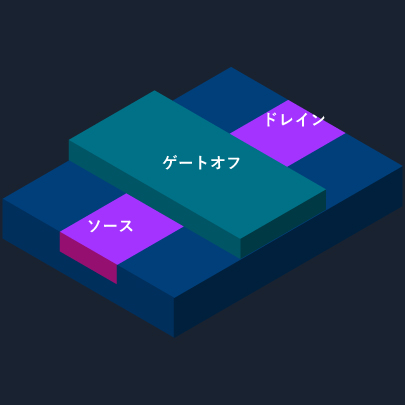

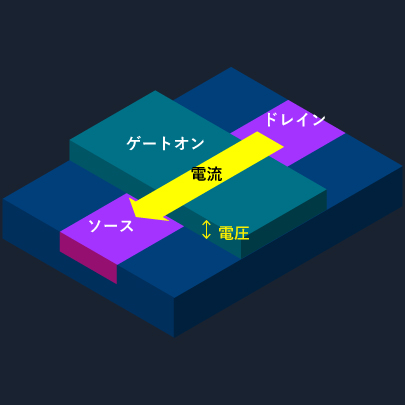

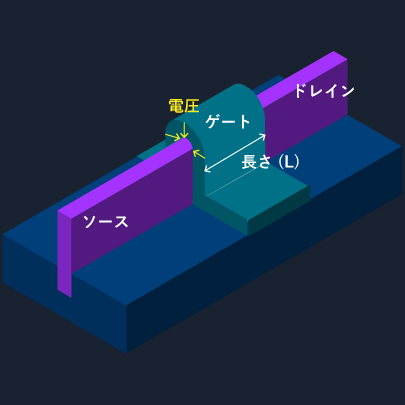

図はMOSFETです。図2はゲートがオフ(電圧がかかっていない)状態なので電流は流れません。図3はゲートがオン(電圧がかかっている)状態なのでドレインからソースへ電流が流れます。ゲート電圧のあり/なしが、スイッチのオン/オフになっています。

MOSFETの最大の特徴は「小さくできる」ことです。ここ50年の間にプレーナ型MOSFETが劇的な微細化を遂げてきました。

図はMOSFETです。図2はゲートがオフ(電圧がかかっていない)状態なので電流は流れません。図3はゲートがオン(電圧がかかっている)状態なのでドレインからソースへ電流が流れます。ゲート電圧のあり/なしが、スイッチのオン/オフになっています。

図2 プレーナ型MOSFET(スイッチオフ)

図3 プレーナ型MOSFET(スイッチオン)

プロセス

半導体の製造工程を「プロセス」と呼び、半導体の微細化を表す指標を「プロセスノード」と呼びます。

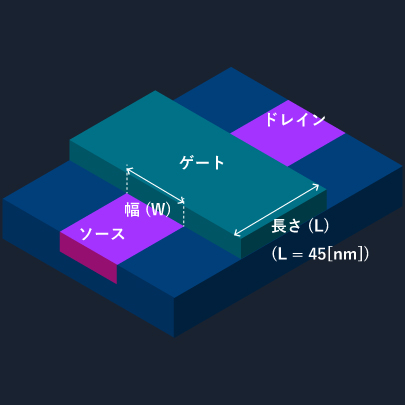

例えば、プロセスノード45ナノはトランジスタの長さ(L)の最小値が45nm(ナノメートル)で半導体を製造することを意味します。プロセスノードは、この半導体がどういう性能でどのくらいの集積度があるのかを示す指標として使われています。プレーナ型MOSFETは、50年の歳月をかけてムーアの法則(※)にのっとり、プロセスノードをマイクロ(1000分の1mm)からナノ(100万分の1mm)へと劇的に微細化を遂げました。

※ムーアの法則:1965年にインテル社の共同創業者であるゴードン・ムーア氏が「半導体回路の集積度は、約1年半〜2年で2倍になる」というムーアの法則を提唱します。

例えば、プロセスノード45ナノはトランジスタの長さ(L)の最小値が45nm(ナノメートル)で半導体を製造することを意味します。プロセスノードは、この半導体がどういう性能でどのくらいの集積度があるのかを示す指標として使われています。プレーナ型MOSFETは、50年の歳月をかけてムーアの法則(※)にのっとり、プロセスノードをマイクロ(1000分の1mm)からナノ(100万分の1mm)へと劇的に微細化を遂げました。

※ムーアの法則:1965年にインテル社の共同創業者であるゴードン・ムーア氏が「半導体回路の集積度は、約1年半〜2年で2倍になる」というムーアの法則を提唱します。

図4 45ナノプロセス MOSFET

ところが、プロセスノードが22nmあたりになると、プレーナ型MOSFETの平面的な構造ではこのクラスの微細化に耐えられず、電流が漏れてスイッチにならないという問題が出てきました。

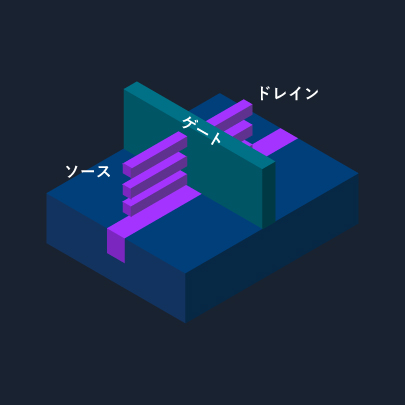

ここで登場するのが、フィン型MOSFET「FinFET(フィンフェット)」です。3ナノ半導体FinFETは、アップル社のM4にも使われていて、T社熊本第2工場でも生産されようとしています。

ここで登場するのが、フィン型MOSFET「FinFET(フィンフェット)」です。3ナノ半導体FinFETは、アップル社のM4にも使われていて、T社熊本第2工場でも生産されようとしています。

FinFET(フィンフェット)

薄いフィン形状の素子をゲートで囲むFinFETは、スイッチを立体にして3方向から電圧をかけることでトランジスタの長さ(L)を短くしなくても性能を上げることができ、かつ微細化による電流が漏れる問題も解決しました。

フィン型はプレーナ型とは異なり、トランジスタの長さ(L)が性能や集積度などを表すプロセスノードとしては適切でなくなりました。

この図の中に3ナノメートルは出てきません。

では、「3ナノプロセス」というプロセスノードは何かというと、「このプロセスで製造した半導体の性能や集積度は、プレーナ型MOSFETの3nmプロセスに相当する」ことのようです。

ですので、今後プロセスノードの名称に「長さ」を使用することはなくなっていくでしょう。インテル社では、Intel7やIntel3といったプロセスノード名を使っています。

フィン型はプレーナ型とは異なり、トランジスタの長さ(L)が性能や集積度などを表すプロセスノードとしては適切でなくなりました。

この図の中に3ナノメートルは出てきません。

では、「3ナノプロセス」というプロセスノードは何かというと、「このプロセスで製造した半導体の性能や集積度は、プレーナ型MOSFETの3nmプロセスに相当する」ことのようです。

ですので、今後プロセスノードの名称に「長さ」を使用することはなくなっていくでしょう。インテル社では、Intel7やIntel3といったプロセスノード名を使っています。

図5 FinFET

次世代の半導体プロセス

半導体プロセスは常に進化しています。FinFETの次は2ナノ半導体に使われる「GAA(Gate-All-Around)」型のMOSFETが発表されています。

そして、その次のオングストローム世代にむけてRIBBON FETやPOWER VIAといった技術が発表されています。

※ オングストローム(Å):100億分の1メートル = 0.1nm

「もう微細化の限界だろう」という壁を半導体業界はいくつも超えてきました。今後も微細化により「高性能」、「高機能」、「省電力」、「省スペース」という利益を世界に与え続けるでしょう。当社も半導体業界の一員として、プロセスの進化に乗り遅れることなく、この「価値」をお客さまへ提供し続けてまいります。

そして、その次のオングストローム世代にむけてRIBBON FETやPOWER VIAといった技術が発表されています。

※ オングストローム(Å):100億分の1メートル = 0.1nm

「もう微細化の限界だろう」という壁を半導体業界はいくつも超えてきました。今後も微細化により「高性能」、「高機能」、「省電力」、「省スペース」という利益を世界に与え続けるでしょう。当社も半導体業界の一員として、プロセスの進化に乗り遅れることなく、この「価値」をお客さまへ提供し続けてまいります。

図6 GAA

資料

- 台湾の半導体受託製造最大手、TSMC(台湾積体電路製造)は2026年2月5日、熊本県菊陽町で建設中の第2工場で回路線幅3ナノメートル(ナノは10億分の1)の最先端半導体を国内で初めて量産する計画を日本政府に伝えた。

- 読売新聞によると日本政府は熊本第2工場建設に7320億円の補助を決めている。、設備投資の規模は170億ドル(約2兆6000億円)に上る見込み。

- TSMCの3nmプロセス

- 半導体のプロセスルールについての補足

https://zenn.dev/takenobu_hs/articles/2acdcd8bce0286

![[ロゴ]三栄ハイテックス株式会社](/shared/img/logo_w.png)